[Module Structure] module example_code #(parameter D=10)( inputwire[3:0]i, outputwire[3:0]o ); wiretmp; wirerst; ANDA1(i, tmp); assign o = ~i; always @(*) begin if(rst) tmp = 1'b0; end endmodule ※ 임의로 만든 모듈이기 때문에 제대로 작동하는지 아닌지는 판별 불가. 단순히 이렇게 모듈을 작성한다라는 것을 인지하면 되겠습니다. 한 가지 주의할 점은 assign 혹은 always와 같은 것을 사용하여 식을 정의할 때, 사용하는 변수가 그 이전에 선언이 되어야합니다. 즉, 위 모듈에서 선언 파트는 wire tmp; ~ wire rst;인데, 이 부분이 선언이..

- Bunch of Variables or Nets를 말하며, 선 다발(Bus)을 의미한다. 기본적인 선언 [Left Range : Right Range] reg [0:7] A, B; // Two 8 bit reg with MSB as the 0th bit wire [3:0] Data; // 4 bit wire with MSB as the 4th bit modulecter( inputwirerst, inputwireclk, inputwirejmp, inputwire[3:0]jump, outputrg[3:0]count // 3-bit counter module ); always @(posedge clk) // sync logic begin if(rst)count = 0; // reset signal is ..

학부 때 했던 프로젝트와 코딩을 이번에 포트폴리오 다시 작성하며 정리한건데 참... 워드로 작성은 다 한 상태인데 이걸 블로그에 올리려니 또 문제가 되네요. 아무래도 코딩을 직접적으로 쓰게 된다면 추후 누군가 대학에서 프로젝트를 할 때 베끼게 될 수가 있으니... 최대한 코딩은 안 쓰는 방식으로 정제를 한 번 해야할 듯 합니다.

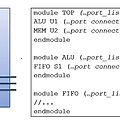

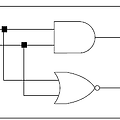

다음의 블록을 생성하고자 할 때 Verilog가 어떻게 사용되는지를 보자. module mod1( inputwire [1:0]A, outputwireB, outputwireC ); assignB =A[0] & A[1]; assignC = ~(A[0] | A[1]); endmodule 인풋 A와 아웃풋 B, C가 존재하고, 블록 내부에서는 인풋 A에 의해 아웃풋 B가 결과로 나오게 되는 AND 게이트와 아웃풋 C가 결과로 나오는 NOR 게이트가 구성되어 있다. 그렇다면 현재 위 코드에서 사용된 wire가 무엇인지를 정의할 필요가 있습니다. Verilog에서는 wire와 reg를 통해 타입을 규정하게 됩니다. 그 중 wire는 값을 저장할 수 있고, reg는 레지스터와 같이 값을 저장할 수 있음을 말합니다...

ASIC은 Application Specific Integrated Circuit의 준말로, 특정한 목적과 기능을 위해 맞춰진 집적회로(IC)를 말한다. 즉, 주문형 반도체는 고객의 목적을 위해 필요한 기능을 수행하도록 제작되는 것을 말한다. 이러한 반도체를 만들기 위해서는 일반적인 설계 과정이 존재할 수 밖에 없는데 다음과 같다. 1. Application : 어떠한 목적을 가진 칩을 만들것인가? 2. Specifiaction : 요구되는 목적과 성능을 위해 칩을 어떻게 구성할 것인가? - 비단 반도체 업계에서만 그러는 것이 아닌, 공학 분야에 적용되는 단계이다. 최종 결과를 뽑아내기 위해서는 그에 알맞은 스펙을 명확하게는 아니여도 추상적으로는 머릿속으로 그려볼 수 있어야 한다. 이 단계에서는 추상적으..

Lost Memory 【Pop Candy Wonderland 앨범】 채보 기간 : 23.04.08 ~ 23.05.28 --------------------------------- 취미로 하는 건반가지고 뚱땅뚱땅하는거였지만 그래도 목표 하나를 가지고 채보 완성해보자는 생각으로 오랫동안 만지고 있던 곡이네요. 이전에 귀카피를 하였던게 군입대하기 전이었던 2017년이니까 되게 오랜만에 그리고 조금이나마 체계적으로 카피해본 두번째 곡입니다. 페달링이라던가 셈여림이라던가 부족한게 많이 있지만 그래도 완성했다는 것에 의의를 두고 있어요.