기본적으로 C에서 사용하는 연산자를 따라가는 편이다.

그렇다해도 나는 Verilog 사용자가 C를 보면서 공부하는건 아닌거 같아서 따로 정리하고자 한다.

[Relational Operations : 비교 연산자]

메인으로 사용되는 표현식

| < | A < B | A가 B보다 작은가? |

| > | A > B | A가 B보다 큰가? |

| >= | A >= B | A가 B보다 크거나 같은가? |

| <= | A <= B | A가 B보다 작거나 같은가? |

해당 연산은 비교 연산자(Relation Operations)로 1: 참, 0: 거짓, X : Unknown으로 셋 중 하나가 나오게 된다.

) 이 중 하나라도 X 혹은 Z 비트가 존재한다면 나오게 되는 값은 무엇인가?

=> X가 반환된다. X이든 Z이든 내가 비교하려는 대상이 명확하지 않기 때문이다.

[Arithmetic Operations : 산술 연산자]

| * | C = A * B | 곱 |

| + | Sum = A + B | 합 |

| - | Diff = A - B | 차 |

| ** | Pow = A ** B | 제곱(A의 B승) |

| / | C = A / B | 나누기(int<정수> 형) |

| % | AmodB = A % B | 모듈러(나머지) |

(**, /, %) 연산자는 일반적으로 회로 기술하는데 사용하지 않는다. 만일 필요하다고 한다면, 제곱을 하는, 나눗셈을 하는, 나머지 연산을 하는 회로를 직접 구현할 필요가 있다. Why? 합성의 대상이 되지 않는다.

[Logical Operations : 논리 연산자]

| && | A && B | A 그리고 B가 참인가? |

| || | A || B | A 혹은 B가 참인가? |

| ! | if (!A) C= B | A가 참이 아니라면 B는 C에 할당된다. |

[Equality & Identity Operations]

| C == A | Logical Equality |

| C === A | Literal Equality Considering 4-Value Logic |

| C != A | logical Inequality |

| C !== A | Literal Inequality 4-Value Logic |

단, (===) 연산자는 합성이 불가능하다.

이 연산자가 어떻게 작용되는지는 아래 예제를 보자.

module Operator;

reg [4:0] A;

reg [4:0] B;

initial begin

A = 5'h1x; // A = 5'b1_xxxx;

B = 5'h1x; // B = 5'b1_xxxx;

$display("%b", A==B); // X

$display("%b", A===B); // 1

end

endmodule

== 연산자는 x부분을 파악할 수 없으니 x가 나오게 될 것이고, ===연산자는 말 그대로 비교를 하는 것이기 때문에 1이 나오게 된다.

[Bitwise & Reduction Operations]

| & | B = &A | A의 모든 비트를 AND 연산해 B에 할당 |

| | | B = |A | OR 연산 |

| ^ | B = ^A | XOR 연산 |

[미안하다. 사실 이거 작성하려고 이렇게 관심을 끌었다.]

EX)

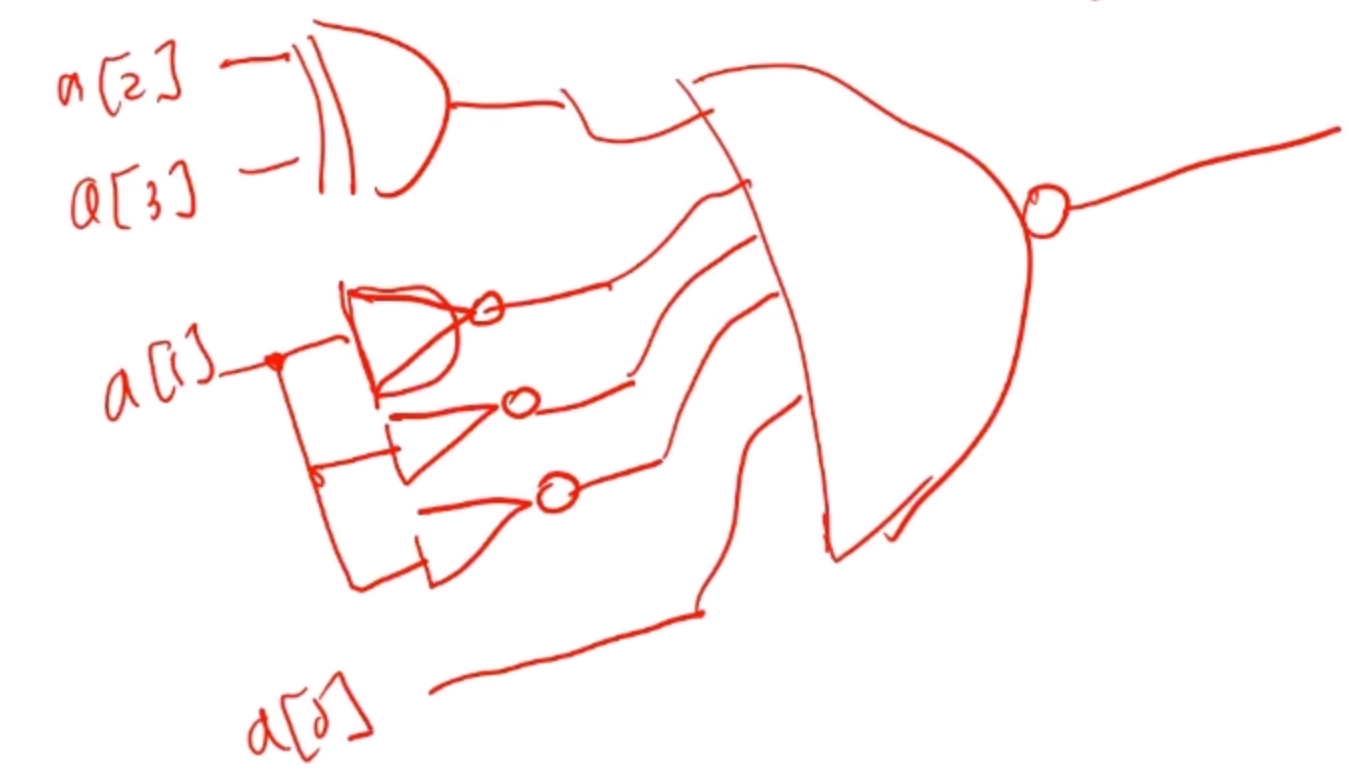

| ~| {a[0], ~{3{a[1]}}, ^{a[2], a[3]}} |

Verilog에서 { _ , _ } 중괄호는 어떠한 역할을 하는가? 라는 것을 정리하려고 위 연산자를 이렇게 주저리주저리 썼다.

결론부터 말하자면, 콤마(,)로 이어진 것을 접합해준다.

'무슨 개소리냐'라고 넘길 것이 아니라 차근차근 살펴보자.

a[0]은 어떠한 연산자도 붙어있지 않기 때문에 그냥 와이어라고 생각한다.

다음 a[1]은 3배임을 알 수 있기 때문에 3개의 Gate를 만들고 (~)가 있기 때문에 not을 붙인다.

a[2]와 a[3]은 중괄호로 묶여있기 때문에 이를 하나로 묶어주는데 (^:XOR)를 확인하고 XOR로 묶는다.

마지막으로 이 Gate가 전부 중괄호 안에 묶여있기 때문에 하나로 합치는데 이 때 (|:OR)를 확인하고 OR로 묶고 이를 다시 (~) not을 붙이면 해당 예제는 끝이 난다.

연산자는 당장 구글에 쳐봐도 어떻게 사용하는지 나오기 때문에 간단하게 표만 만들어 사용 방법만 작성하였지만,

해당 { _, _ } 중괄호는 여러 번 사용해봐야 숙지가 된다.

[Shift & Other Operations]

| << | a<<1 | shift left a by 1 bit |

| >> | a>>1 | shift right a by 1 bit |

| <<< | b<<<1 | arithmetic shift by 1 |

| >>> | b>>>1 | arithmetic shift by 1 |

| ?: | c = sel ? a : b | sel이 참일 때, c = a, 거짓일 때, c = b |

| {} | {co, sum} | = a + b + ci |

| {{}} | b = {3{a}} | replicate N times |

'Verilog' 카테고리의 다른 글

| 6. 게이트 지연(Gate Delay) (0) | 2023.08.17 |

|---|---|

| 5. Continuous Assignments (0) | 2023.07.13 |

| 3. Verilog의 모듈 구조 (0) | 2023.07.13 |

| 2. Verilog의 벡터(Vector) 표현 및 카운터 모듈 예제 (0) | 2023.07.13 |

| 포스팅 할 수 있는게 생기긴 했는데 (0) | 2023.07.11 |